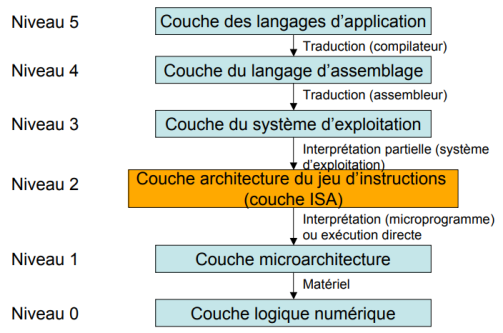

L’ISA (Instruction Set Architecture) est un jeu d’instructions définissant l’ensemble des instructions machines qu’un processeur d’ordinateur peut exécuter, supporter. Ces instructions machines permettent d’effectuer des opérations élémentaires (addition, opérateurs booléens…) ou encore des opérations plus complexes comme la division ou le passage en mode basse consommation. Le jeu d’instructions précise aussi quels sont les registres du processeur manipulables par le programmeur (les registres architecturaux). Ils constituent l’interface entre le matériel et le logiciel : ils définissent les opérations que doit effectuer le matériel et ils sont la cible d’un compilateur.

Différence entre deux types d’ISA : RISC et CISC

Il existe deux types d’ISA :

- RISC (Reduced instruction set computer – Instructions de longueur fixe)

- CISC (Complex instruction set computer – Instructions de longueur variable) comme x86, IA-32, Intel 64

Nous allons aborder les différences entre ces deux types d’ISA en étudiant leur façon dont ils gèrent la multiplication de 2 nombres en mémoire.

La mémoire principale (main memory) est divisée en emplacements numérotés de 1 à 4 pour les colonnes et de 1 à 6 pour les lignes. L’unité d’exécution (execution unit) réalise tous les calculs. Cependant, l’unité d’exécution ne peut exploiter seulement les données qui ont été chargées dans un des six registres (A, B, C, D, E, F).

Supposons que l’on veuille trouver le produit de 2 nombres – l’un stocké à l’emplacement 2:3 et l’autre stocké dans l’emplacement 5:2 – et stocker le résultat dans l’emplacement 2:3.

L’approche CISC

Le but principal de l’architecture CISC est de compléter une tâche en utilisant le moins de lignes d’assembleur possible. Ce qui se fait en construisant un processeur capable de comprendre et d’exécuter une série d’opérations. Pour cette tâche particulière, un processeur CISC contient une instruction spécifique qu’on appellera “MULT”. Cette instruction charge les deux valeurs dans deux registres différents, les multiplie dans l’unité d’exécution et stocke le produit dans le registre approprié. Donc toute la tâche de multiplication de deux nombres peut être complété avec qu’une seule instruction :

MULT 2:3, 5:2

MULT est appelé une “instruction complexe”. Elle exploite directement les banques de mémoire de l’ordinateur et n’a pas besoin que le programmeur appelle explicitement une fonction de chargement ou de stockage. Par exemple, soit “a” le représentant de la valeur à l’emplacement 2:3 et “b” celui de la valeur à l’emplacement 5:2, alors cette commande est identique à l’instruction C “a = a*b”.

L’un des principaux avantages de ce système réside dans le fait que le compilateur fait un tout petit travail de traduction d’instructions d’un langage de haut niveau en assembleur. Ceci est dû à la longueur du code qui est relativement courte, ainsi très peu de RAM est nécessaire au stockage des instructions. L’accent est mis sur la construction d’instructions complexes directement dans le matériel.

L’approche RISC

Les processeurs RISC utilisent de simples instructions pouvant s’exécuter en un cycle d’horloge. Soit, la commande “MULT” décrite dans la partie concernant CISC, serait divisée en trois commandes séparées : “LOAD” qui permet de déplacer les données de la mémoire à un registre, “PROD”, qui trouve le produit entre 2 opérandes situés dans les registres, et “STORE”, qui déplace une donnée d’un registre à un emplacement mémoire. Pour effectuer la même série d’étapes décrite dans l’approche CISC, un programmeur aurait besoin de coder quatre lignes d’assembleur :

LOAD A, 2:3 LOAD B, 5:2 PROD A, B STORE 2:3, A

A première vue, cela semble être une méthode moins efficace d’effectuer l’opération puisqu’il y a plus de lignes de code, ainsi plus de RAM sera nécessaire pour stocker les instructions du niveau de l’assembleur. Le compilateur devra aussi effectuer plus de travail pour convertir une instruction de langage de haut niveau en code de cette forme.

Cependant, la stratégie de RISC apporte aussi quelques avantages importants. Chaque instruction ne nécessite seulement qu’un cycle d’horloge pour s’exécuter, tout le programme s’exécutera avec environ le même temps que la commande “MULT”. Ces instructions RISC nécessitent moins de mémoire hardware que les instructions complexes, ce qui laisse plus de place pour des registres à usage général. Comme toutes les instructions s’exécutent en un temps uniforme (une unité de temps), l’utilisation de pipeline est possible.

Le fait de séparer les instructions “LOAD” et “STORE” réduit en fait la quantité de travail que l’ordinateur doit effectuer. Après qu’une commande “MULT” au style de CISC soit exécutée, le processeur efface automatiquement les registres. Si l’un des opérandes doit être utilisé pour un autre calcul, le processeur devra recharger la donnée à partir de la banque de mémoire dans un registre. Dans RISC, l’opérande restera dans le registre jusqu’à ce qu’une autre valeur soit chargée à sa place.

L’équation de performance

L’équation suivante est communément utilisée pour exprimer la capacité de performance d’un ordinateur:

L’approche CISC tente de minimiser le nombre d’instructions par programme en sacrifiant le nombre de cycles par instruction. RISC fait le contraire, il réduit les cycles par instruction au prix du nombre d’instructions par programme.

Résumé des différences :

| CISC | RISC |

| accent mis sur le matériel | accent mis sur les logiciels |

| multi-clock instructions complexes | single clock instructions réduites seulement |

| memory-to-memory : “LOAD” et “STORE” inclus dans les instructions | register to register : “LOAD” et “STORE” sont des instructions indépendantes |

| code court, nombre de cycles par seconde élevé | code long, faible nombre de cycles par seconde |

Les architectures RISC sont utilisées dans des applications de pointe telles que le traitement de vidéo ou d’image ou encore la télécommunication.

CISC est utilisé dans des applications de plus bas niveau comme dans des systèmes de sécurité ou encore dans la domotique etc.

Exemple de format d’une instruction

Un modèle d’exécution est un couple (n, m) avec n le nombre d’opérandes par instruction et m le nombre d’opérandes mémoire par instruction.

Pour RISC, (n,m) = (3,0), comme les instructions sont de longueur fixe, de type Load and Store (seules instructions mémoires).

Pour CISC (type IA-32), (n,m) ≠ (3,0) car instructions de longueur variable.

Dans notre exemple, nous considérons la somme des éléments d’un tableau de N entiers à l’adresse TAB.

S=0

For (i=0;i<N;i++)

S+=TAB[i];

Exemple RISC (3,0) sur un processeur NIOS II (32 bits)

r2 = &TAB // adresse du tableau dans r2 (r2 est donc l’adresse courante) ADD r1, 0, r0 // ↔ r1 = r0 + 0 = 0, (ici r1 joue le role de S, donc compteur) ADD r3,N,r0 // ↔ r3 = N + r0 = 0, donc N dans r3 (r3=N = borne max) SRLI r3,r3,2 // Décalage de 2 bits à gauche, donc 4*N dans r3 (adresse maximale, un int = 4 octets, processeur 32 bits) ADD r3,r3,r2 //↔ r3 = r3 + r2 → Adresse du mot après TAB[N-1] (borne d’adresse maximale) Boucle : tant que r2<r3 LOAD r4,r2 // chargement de Tab[i]=r2 dans r4 (r4 est le chargeur de TAB[i]) ADD r1,r1,r4 // accumulation : r1 = r1 + r4 ADDI r2,r2,4 // adresse de l’élément suivant : r2 = r2 + 4 // Résultat dans r1

Donc ici : 2 instructions pour accéder à chaque élément du tableau (élément + adressage)

Exemple RISC (3,0) sur un processeur ARM (32 bits)

r2 = &TAB // adresse du tableau dans r2 (r2 est donc l’adresse courante) ADD r0, 0, 0 ↔ r0 = 0, (ici r0 joue le role de S, donc compteur) NB : r0 est différent de 0 dans ARM ADD r1,N,0 // ↔ r1=N, donc N dans r1 (r1=N = borne max) Boucle : tant que r1>0 LOAD r3,[r2],#4 //chargement de Tab[i] + préparation adresse suivante (+4). ARM permet cela ADD r0,r0,r3 // accumulation SUBS r1,r1,#1 // décrémentation compteur de boucle (-1) // Résultat dans r0

Donc ici : 1 seule instruction pour accéder à chaque élément du tableau (élément + adressage en même temps)

Sources

- https://cs.stanford.edu/people/eroberts/courses/soco/projects/risc/risccisc/

- https://www.elprocus.com/difference-between-risc-and-cisc-architecture/

Pierre Bolinches, Hamza Dardouri, Ghita Laoud, Tanina Soualah, Emel Topal